BarsFA - 4-transistor full adder

For my transistor-computer project (which is already going for 3 years) I needed compact implementations for most of common digital blocks, and full adder - is one of the most important among these.Canonical implementation of CMOS full adder takes 28 transistors:

Modern implementations using transmission gate and number of tricks reduce this number down to 8-11, with more strict requirements for transistor selection. These schemes usually could not be used with discrete transistors, as they use 4-terminal transistors, and suffer from degradation of logical 1 level, which becomes even more severe with discrete transistors as they have Vt=1.5-2 compared to ~0.5V for integrated transistors.

The smallest full adder I've seen was using 6 transistors and capacitors at inputs - but I am not sure how to make it work reliable in real-world. Known implementation using bipolar transistors - also using 22 transistors.

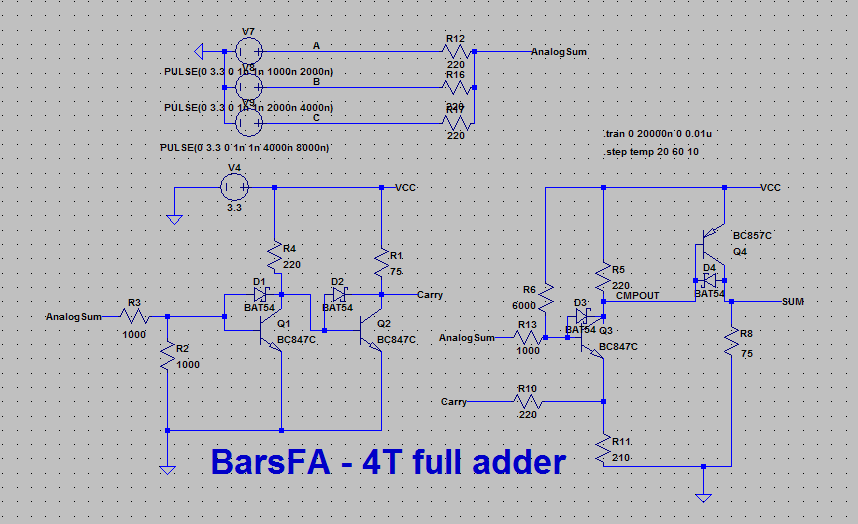

But can you make it using only 4 transistors? After thinking and trying few variants, i've got the following schematic working:

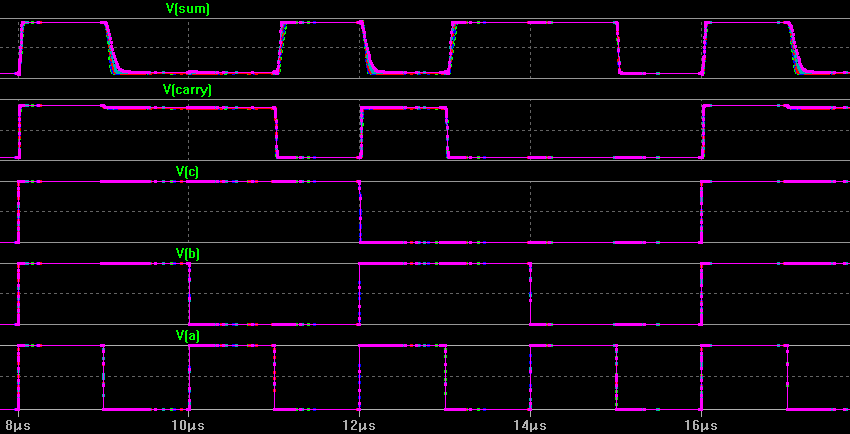

Simulated waveforms:

You can download schematic for simulation in LTspice IV here.

How it works? As order of terms is not important, we can just mix them in analog way, and by tuning threshold voltage of double inverter easily get carry. Then we can subtract carry from analog sum using Q3 - and we are getting sum. Surely, this all requires threshold voltages tuning and simulation across temperature range as it's quite sensitive to transistor selection, resistor values and temperature. Schottky diodes are here to prevent transistor saturation, which significantly reduce performance.

One could use MOSFET's - this will provide better temperature stability, but these transistors must have quite low Vt.

@BarsMonster

@BarsMonster