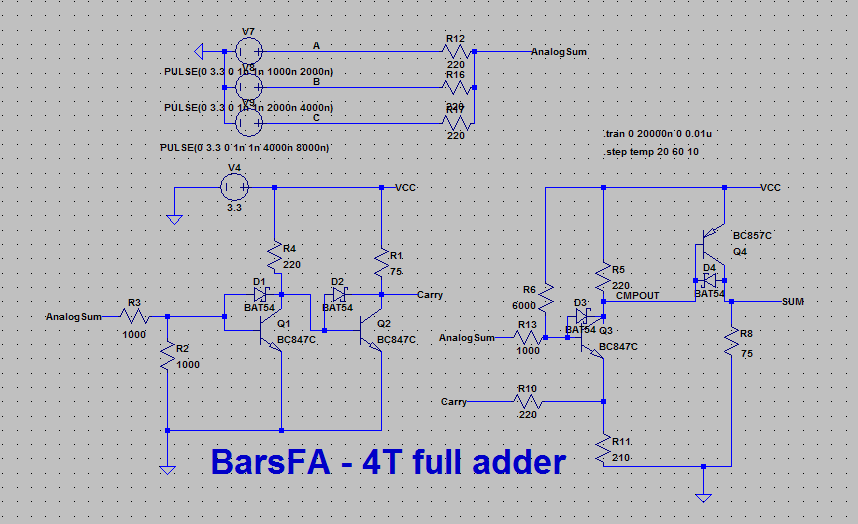

BarsFA - полный сумматор на 4-х транзисторах

Для своего многолетнего хобби-проекта транзисторного компьютера требовались компактные реализации всех основных цифровых блоков, и полный сумматор - один из наиболее важных.Каноническая реализация КМОП полного сумматора - требует 28 транзисторов:

Современные реализации с использованием transmission gate и различных хитростей - требуют 8-11 транзисторов с более жесткими требованиями к выбору транзисторов, но напрямую из дискретных транзисторов эти схемы не реализовать - нужны 4-х выводные транзисторы (а они редкость), и из-за деградации уровня логической 1 нужно высокое напряжение питания (т.к. пороговое напряжение доступных дискретных полевых транзисторов - 1.5-2 вольта против 0.5В у интегральных транзисторов).

Самый минимум, который приходилось видеть - из 6 транзисторов, с использованием конденсаторов (но надежность вызывает вопросы). Известные реализации на биполярных транзисторах - также требуют 22 транзистора.

Но можно ли обойтись всего 4 транзисторами? Я немного пораскинул мозгами, и получилось следующее:

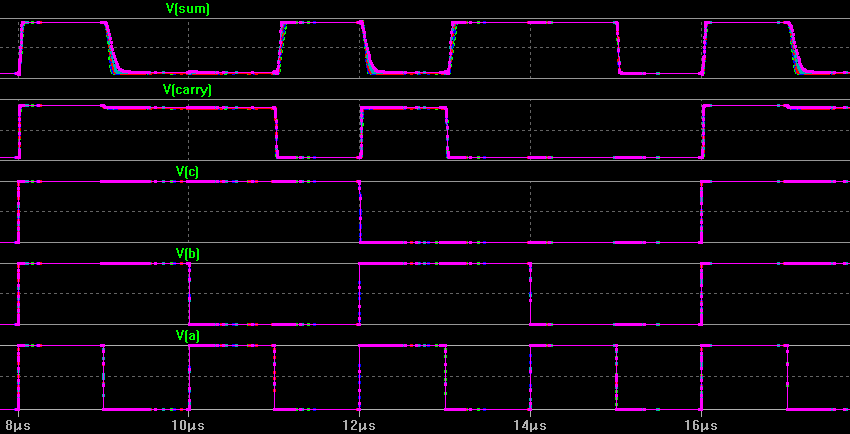

Графики работы:

Схему для симуляции в LTspice IV можно скачать тут.

Принцип работы следующий: т.к. порядок слагаемых не имеет значения, мы их просто аналогово смешиваем, и точно подбирая пороговое напряжение сдвоенного инвертора - сразу получаем перенос. Затем вычитая на транзисторе Q3 из аналоговой суммы перенос - получаем сумму. Конечно, все это требует точного подбора уровней срабатывания, и симуляции с учетом температуры. Диоды Шоттки - для предотвращения входа транзисторов в глубокое насыщение, что резко снижает скорость работы.

Использование полевых транзисторов возможно, и обеспечивает лучшую температурную стабильность, главное чтобы у них было достаточно низкое пороговое напряжение.

@BarsMonster

@BarsMonster